感覺這次教的比較難,用了好久才跑出來,若不是老師的教導,我想我應該也做不出來吧,難度提高的同時,當寫出來的成就感,是無法用言語形容的!

==================================================================

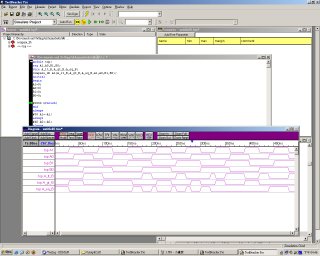

module top;

reg [15:0] a,b;

reg c_in;

wire [15:0] sum;

wire c_out;

Add_rca_16 m1(sum,c_out,a,b,c_in);

initial

begin

a=0;

b=0;

c_in=0;

#2000 $finish;

end

always

#100 a[0]=~a[0];

always

#150 b[1]=~b[1];

always

#200 c_in=~c_in;

endmodule

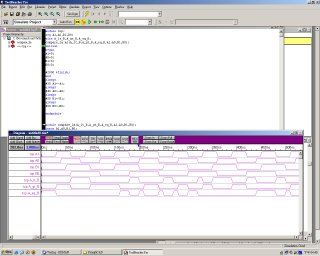

module Add_rca_16 (sum,c_out,a,b,c_in);

output [15:0] sum;

output c_out;

input [15:0] a,b;

input c_in;

wire c_in,c_in4,c_in8,c_in12,c_out;

Add_rca_4 M1(sum[3:0], c_in4, a[3:0], b[3:0], c_in);

Add_rca_4 M2(sum[7:4], c_in8, a[7:4], b[7:4], c_in4);

Add_rca_4 M3(sum[11:8], c_in12, a[11:8], b[11:8], c_in8);

Add_rca_4 M4(sum[15:12], c_out, a[15:12], b[15:12], c_in12);

endmodule

module Add_rca_4(sum,c_out,a,b,c_in);

output [3:0] sum;

output c_out;

input [3:0] a,b;

input c_in;

wire c_in4,c_in3,c_in2;

Add_full G1 (sum[0],c_in2,a[0],b[0],c_in);

Add_full G2 (sum[1],c_in3,a[1],b[1],c_in2);

Add_full G3 (sum[2],c_in4,a[2],b[2],c_in3);

Add_full G4 (sum[3],c_out,a[3],b[3],c_in4);

endmodule

module Add_full(s,c_out,a,b,c_in);

output s,c_out;

input a,b,c_in;

wire s1,c1,c2,c_out_bar;

Add_half G1(s1,c1,a,b);

Add_half G2(s,c2,s1,c_in);

norf201 G3(c_out_bar,c1,c2);

invf101 G4(c_out,c_out_bar);

endmodule

module Add_half(s,c,a,b);

output s,c;

input a,b;

wire c_bar;

xorf201 G1(s,a,b);

nanf201 G2(c_bar,a,b);

invf101 G3(c,c_bar);

endmodule

module xorf201(O,A1,B1);

input A1,B1;

output O;

xor(O,A1,B1);

specify

specparam

Tpd_0_1=1.13:3.09:7.75,

Tpd_1_0=0.93:2.50:7.34;

(A1=>O)=(Tpd_0_1,Tpd_1_0);

(B1=>O)=(Tpd_0_1,Tpd_1_0);

endspecify

endmodule

module nanf201(O,A1,B1);

input A1,B1;

output O;

nand(O,A1,B1);

specify

specparam

Tpd_0_1=1.13:3.09:7.75,

Tpd_1_0=0.93:2.50:7.34;

(A1=>O)=(Tpd_0_1,Tpd_1_0);

(B1=>O)=(Tpd_0_1,Tpd_1_0);

endspecify

endmodule

module invf101(O,A1);

input A1;

output O;

not(O,A1);

specify

specparam

Tpd_0_1=1.53:4.09:6.75,

Tpd_1_0=0.53:4.50:6.34;

(A1=>O)=(Tpd_0_1,Tpd_1_0);

endspecify

endmodule

module norf201(O,A1,B1);

input A1,B1;

output O;

nor(O,A1,B1);

specify

specparam

Tpd_0_1=1.13:3.09:7.75,

Tpd_1_0=0.93:2.50:7.34;

(A1=>O)=(Tpd_0_1,Tpd_1_0);

(B1=>O)=(Tpd_0_1,Tpd_1_0);

endspecify

endmodule