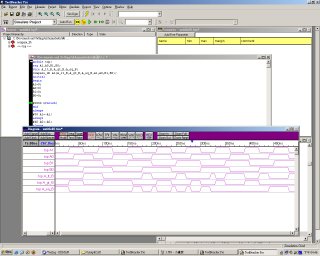

2位元比較器之compare_2b

module top;

reg A1,A0,B1,B0;

wire A_lt_B,A_gt_B,A_eq_B;

compare_2b m1(A_lt_B,A_gt_B,A_eq_B,A1,A0,B1,B0);

initial

begin

A1=0;

A0=0;

B1=0;

B0=0;

#2000 $finish;

end

always

#30 A1=~A1;

always

#40 A0=~A0;

always

#50 B1=~B1;

always

#60 B0=~B0;

endmodule

module compare_2b(A_lt_B,A_gt_B,A_eq_B,A1,A0,B1,B0);

input A1,A0,B1,B0;

output A_lt_B,A_gt_B,A_eq_B;

assign A_lt_B=({A1,A0}<{B1,B0}); assign A_gt_B=({A1,A0}>{B1,B0});

assign A_eq_B=({A1,A0}=={B1,B0});

endmodule

0 Comments:

Post a Comment

<< Home