C++之吊橋參考

經過老師的這次講解,讓我之前學的C++語言有更深入的了解,也使我對期末的報告有新的一番體悟,吊橋的原理其實不會太難,只要認真的去思想,很多難題都可以迎刃而解,勢如破竹!

其實最大的功勞,是老師教的太好了,簡直是學術界的教學楷模!帥啦

===============================================

http://www.isr.umd.edu/~austin/book.d/code.d/c.d/prog_cable.c

經過老師的這次講解,讓我之前學的C++語言有更深入的了解,也使我對期末的報告有新的一番體悟,吊橋的原理其實不會太難,只要認真的去思想,很多難題都可以迎刃而解,勢如破竹!

這週老師所給予的作業,依究不太清楚,還是參考上禮拜而做出來的,不過相信,到後面會越來越熟悉這門課。

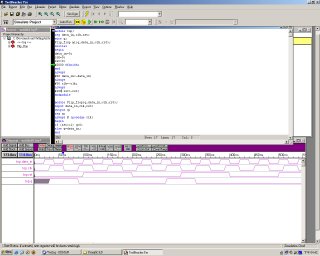

本次上課,我對verilog這門課,有進一步的了解,但很多基本的語言,都不能夠理解,大多都是參考別人而作出來的。所以有空我打算去借一本中文書,把基礎打好,使自己能更為融入這門學問。